Cortex-M7 MCU: Performance Data & Key Specs Overview

The Cortex-M7 MCU class typically delivers multi-hundred-MHz single-core throughput, hardware DSP acceleration, and optional floating-point units, making it a common choice for compute-intensive real-time embedded tasks.

This brief gives engineers a concise, actionable overview of measured performance and the key specs to evaluate when selecting a Cortex-M7-class device for demanding control, signal-processing, and sensor-fusion systems.

Focus is on measurable impacts — latency, sustained throughput, and deterministic behavior — turning lab results into reliable selection criteria.

Background: Where the Cortex-M7 MCU Fits in Embedded Design

Architecture Snapshot — What to Expect

Designers should expect a deeply pipelined, high-instruction-throughput core with a six-stage pipeline, optional single- or double-precision FPU, and a rich DSP instruction set for MAC and SIMD operations. Implementations commonly offer I- and D-cache, optional tightly-coupled memory (TCM), and high-speed flash interfaces.

Typical Application Domains

Cortex-M7-class silicon is suited to motor control with complex controllers, audio/voice DSP, advanced sensor fusion and IMU filtering, real-time vision pre-processing, industrial motion control, and high-speed communications stacks.

Benchmarks & Real-World Performance Measurements

Standard Synthetic Benchmarks

Recommended synthetic benchmarks are CoreMark and Dhrystone for general integer throughput. Measurements should record CPU clock, compiler and optimization flags, and cache enablement.

Measurement Methodology: Run each test at the target clock with -O3 optimizations, record CoreMark over multiple runs, measure FPU kernels with isolated inputs, toggle cache/TCM modes, and report mean, standard deviation, and worst-case latency.

Representative Real-World Workloads

- ● FIR/IIR Filtering Chain

- ● Floating-Point PID Control

- ● IMU Sensor-Fusion (EKF)

- ● Crypto/AES Throughput

Key Specs Deep-Dive: What Drives Performance

Core and memory specs dominate sustained and peak performance. Clock frequency, FPU precision, and DSP support are critical for heavy computational tasks.

| Spec | Design Impact | Measurement to Run |

|---|---|---|

| FPU Type (Single/Double) | FP kernel latency and code density | FPU microbenchmark cycles/op |

| I/D Cache Sizes | Instruction/data fetch stalls | Cache miss rate, CoreMark variance |

| TCM Size | Deterministic low-latency code/data | Compare ISR latencies with/without TCM |

| Flash Interface BW | Sustained code fetch and boot times | Flash read throughput under DMA |

Software Optimizations

- Choose aggressive compiler optimizations (-O3).

- Use intrinsics or assembly for critical MAC loops.

- Place hot code/data in TCM.

- Align to cache lines to reduce thrash.

System-Level Optimizations

- Maximize DMA for bulk transfers to free CPU.

- Partition deterministic code into TCM.

- Minimize frequent bus contention via arbitration.

- Validate clock-tree choices vs thermal envelope.

Selection Checklist & Integration

Decision Criteria

Choose Cortex-M7 when project targets demand high single-core DSP/FPU throughput, deterministic low latency, and sustained memory bandwidth.

Engineering Deliverables

- Spec comparison matrix

- Baseline benchmark document

- Integration risk register

- Thermal throttling profiles

Summary

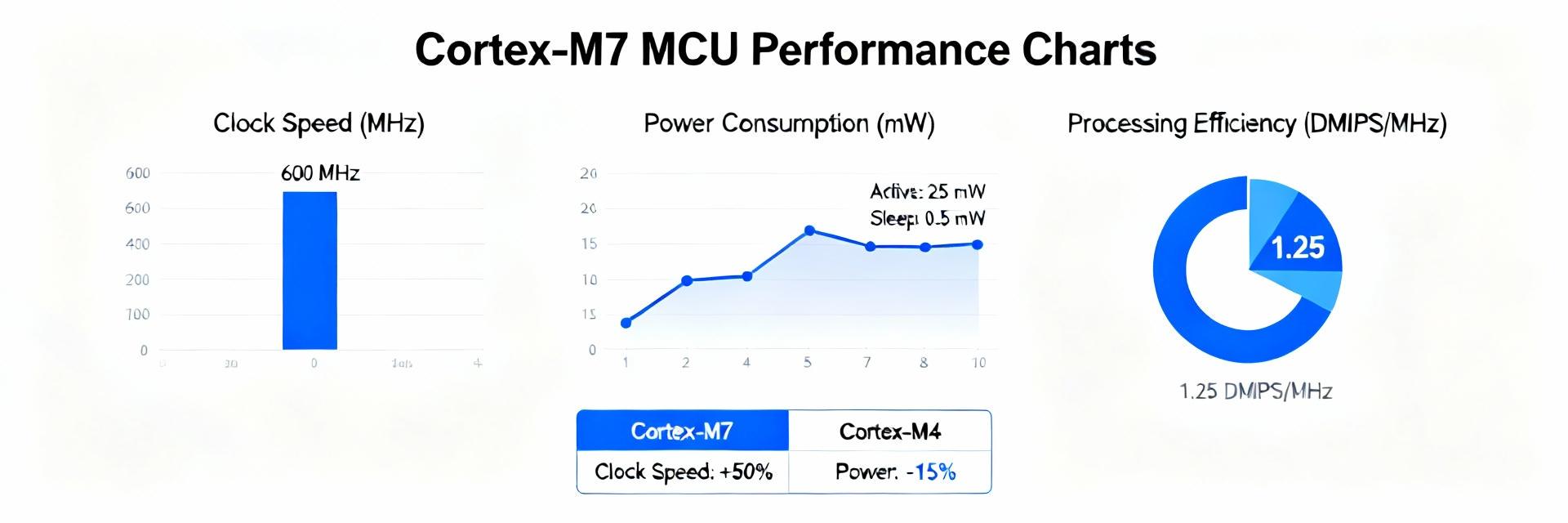

The Cortex-M7 MCU class delivers a mix of DSP/FPU acceleration and multi-hundred-MHz single-core performance. Engineers should focus on three primary decision drivers:

- Core & Memory: Measure cache miss rates and TCM hits to reveal fetch bottlenecks.

- Peripheral/DMA: Benchmark DMA rates and interrupt latency under full load.

- Optimization: Prioritize TCM placement and intrinsics for hot DSP loops.