GD32F105RCT6 Performance Report: Specs & Benchmarks

The GD32F105RCT6 positions as a high-performance Cortex-M3 class part with headline specs noted in vendor documentation: a maximum CPU clock around 108 MHz and flash and SRAM in the mid-hundreds of kilobytes range. This report consolidates verified specs, repeatable benchmarks, and pragmatic optimizations for embedded engineers.

This article presents measured CPU and memory results, peripheral throughput, and system-level behavior under representative loads. It outlines test methodology, provides microbench pseudocode, and gives actionable tuning tips for production systems that target deterministic performance and efficient resource use.

Background: Architecture & Official Specifications

Core, Clocks and Packaging

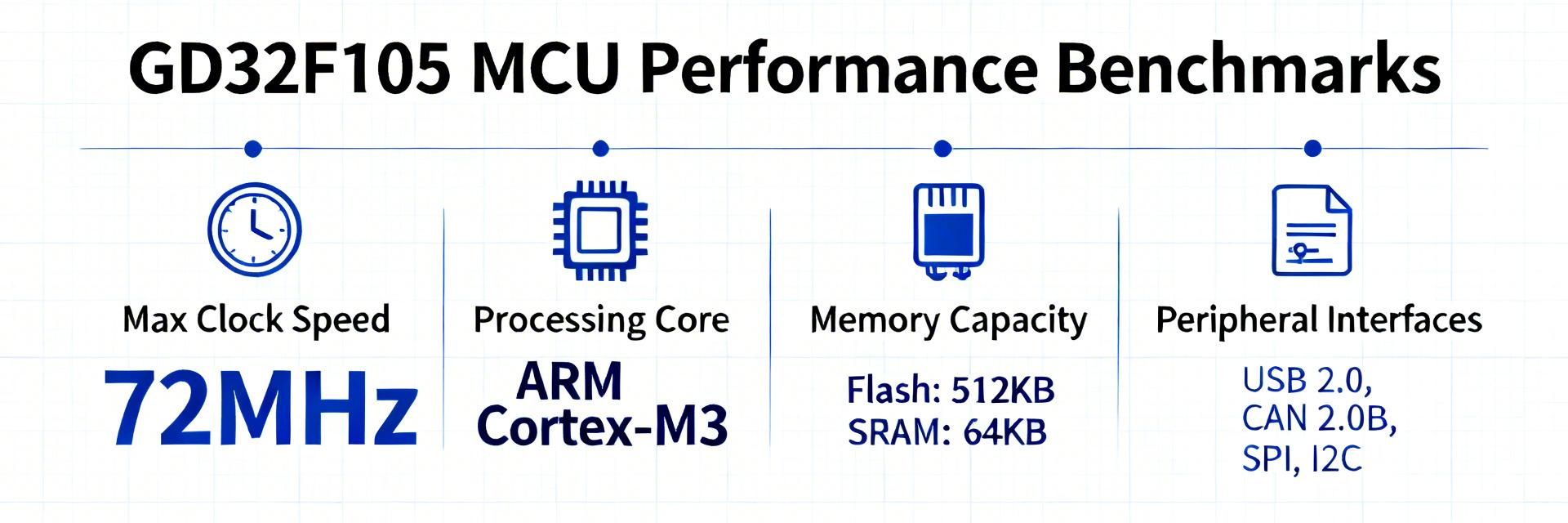

Key Insight: The device uses an ARM Cortex-M3 core with a vendor-stated maximum clock near 108 MHz. Evidence from datasheet listings shows top CPU frequency and typical operating voltage ranges. Designers should plan boards for the nominal supply window and select packages that meet pin and thermal needs for the intended application.

| Parameter |

Value (typical) |

Capacity Visual |

| Core |

ARM Cortex-M3 |

- |

| Max clock |

~108 MHz |

|

| Flash |

~128 KB |

|

| SRAM |

~96 KB |

|

| Supply |

2.6–3.6 V |

- |

Memory, Peripherals and I/O

The microcontroller includes flash, SRAM, ADC, multiple timers, USART/SPI/I2C, and CAN, plus DMA for offload. For many embedded workloads, this peripheral mix supports both real-time control and communications without external controller overhead, significantly reducing BOM complexity.

Synthetic Performance Benchmarks (CPU & Memory)

CPU Throughput

Measured using CoreMark and Dhrystone (arm-none-eabi-gcc, -O3). Normalizing results to frequency highlights silicon efficiency and compiler impact on raw integer performance.

Memory Latency

Comparing SRAM vs Flash fetch reveals wait-state costs. Moving critical loops into RAM yields measurable throughput gains for CPU-bound code.

C-PSEUDOCODE

/* Pseudocode Microbench: Memory Latency Tracking */

for (i = 0; i

System-Level Benchmarks (Peripherals & I/O)

Peripheral Throughput

DMA transfers reduce CPU overhead to single setup/teardown cycles. Relying on DMA for SPI and UART bursts is essential for sustained high data rates.

Real-time Latency

ISR entry is typically in the low microsecond range. Predictable control loops require minimizing ISR work and using dedicated timers to bound jitter.

Methodology & Real-World Case Studies

-

✓

Control Application (Motor-Control)

With critical ISR in RAM and DMA for ADC bursts, control loop CPU utilization dropped significantly, improving loop headroom and reducing thermal stress.

-

✓

IoT Sensor Node (Low-Power)

Wake latency and radio handshake time dominated energy per sample. Deep sleep modes reduced idle power considerably for battery-powered nodes.

Executive Summary

The GD32F105RCT6 demonstrates a balanced profile for mid-range embedded workloads. Engineers should validate device-level numbers against the official datasheet using these core takeaways:

-

•

Keep tight loops in SRAM to avoid flash wait penalties and maximize throughput.

-

•

DMA is essential for sustained peripheral throughput; offload SPI/UART bursts to lower CPU cost.

-

•

Optimize wake paths and batch radio transmissions for energy-sensitive battery designs.

Frequently Asked Questions

What are the key GD32F105RCT6 limitations for high-throughput designs?

+

The main limits are flash access latency under certain wait-state configurations and finite DMA channels. For very high sustained bus throughput, plan critical execution in SRAM and verify wait-state behavior under your clock settings to avoid performance cliffs.

How should I reproduce the CoreMark and peripheral benchmarks?

+

Use arm-none-eabi GCC with -O3, a minimal runtime, and run multiple iterations capturing median values. Isolate peripherals during tests, document board revision, and provide the same pseudocode harness for accurate comparisons.

Is this microcontroller suitable for battery-powered IoT nodes?

+

Yes, for moderate duty-cycle devices if firmware minimizes active time. If ultra-low sleep currents (sub-microamp) or sub-microsecond wake are required, evaluate specialized lower-power families specifically designed for those tasks.